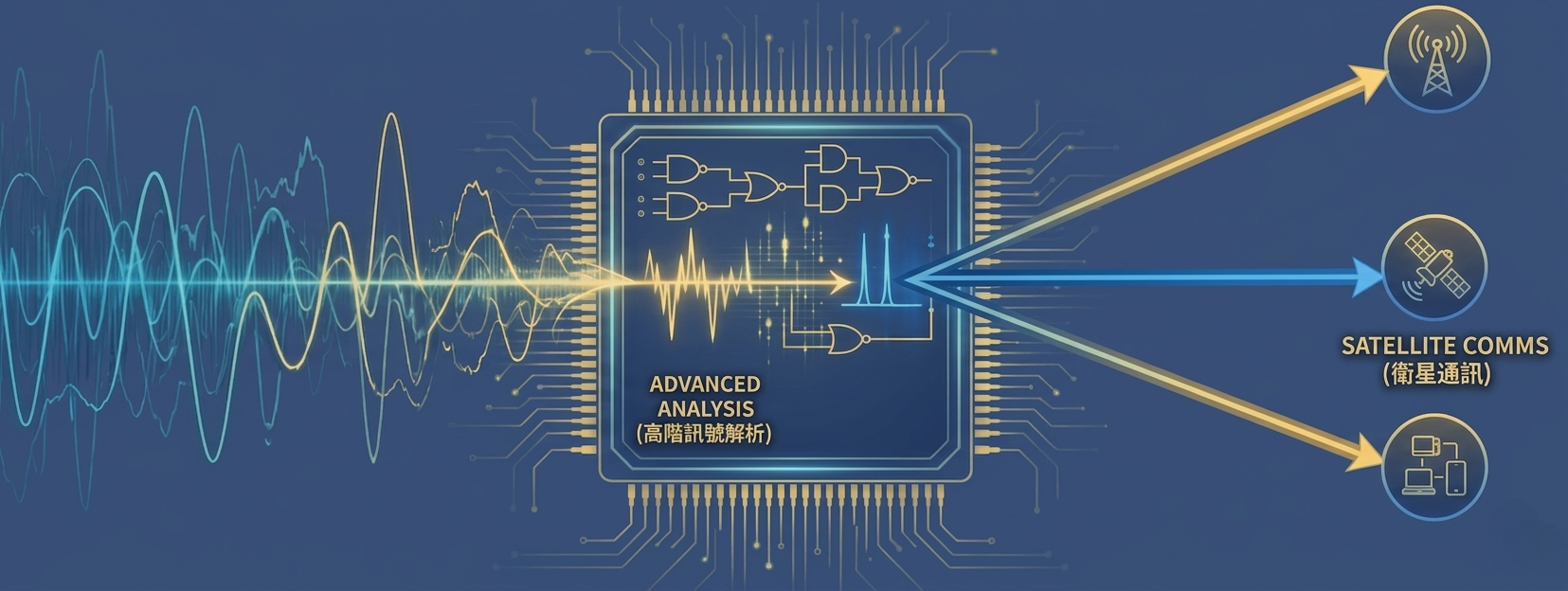

關鍵功能模組設計 (Logic & Software Design)

1. PL 端:全硬體交易流水線 (The Fast Path)

數據封包不進入 CPU,直接在 FPGA 內部完成所有交易步驟:

-

Ultra-low Latency MAC/PCS:自研或優化過的 10G 控制器,減少物理層延遲。

-

FIX/FAST HW Parser:全硬體協議解析邏輯,直接從串流中提取價格與數量。

-

Pre-trade Risk Engine:毫秒級硬體風控(如:單筆上限、部位檢查),確保訂單合規。

-

Binary Order Encoder:將決策結果快速封裝為交易所規範之二進位封包。

2. PS 端:即時管理與監控 (The Control Plane)

-

Real-time OS:搭載具備 RT-Patch 的 Petalinux。

-

策略配置:透過 AXI-Lite 接口將策略參數(如買賣價格上限)動態寫入 PL 暫存器。

-

CMS 後台:提供 Web API,方便管理者遠端監測交易流量與硬體健康狀態。

延遲目標與驗證 (Latency Benchmarking)

-

Tick-to-Trade 目標: < 5$\mu$s (從數據進入網卡到訂單離開網卡)。

-

確定性要求: 延遲抖動 (Jitter) 需控制在 100ns 以內。

-

驗證方式: 使用高精度示波器搭配網路分路器 (Network Tap),進行實體層延遲比對。